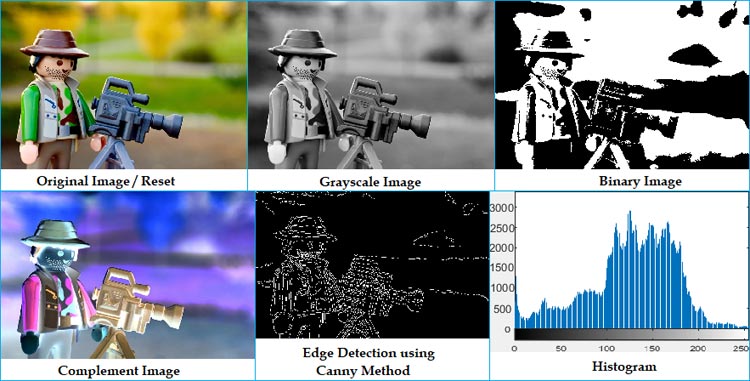

- // Internal Signals //- parameter sizeOfWidth = 8 // data width parameter sizeOfLengthReal = 1179648 // image data : 1179648 bytes: 512 * 768 *3 // local parameters for FSM localparam ST_IDLE = 2'b00,/ / idle state ST_VSYNC = 2'b01, // state for creating vsync ST_HSYNC = 2'b10, // state for creating hsync ST_DATA = 2'b11 // state for data processing reg cstate, // current state output reg DATA_R0, // 8 bit Red data (even) output reg DATA_G0, // 8 bit Green data (even) output reg DATA_B0, // 8 bit Blue data (even) output reg DATA_R1, // 8 bit Red data (odd) output reg DATA_G1, // 8 bit Green data (odd) output reg DATA_B1, // 8 bit Blue data (odd) // Process and transmit 2 pixels in parallel to make the process faster, you can modify to transmit 1 pixels or more if needed output ctrl_done // Done flag Used to be a horizontal synchronous signals for writing bmp file. output reg HSYNC, // Horizontal synchronous pulse // An HSYNC indicates that one line of the image is transmitted. Just create and is not used, will be used once a video or many images are transmitted. Input HCLK, // clock input HRESETn, // Reset (active low) output VSYNC, // Vertical synchronous pulse // This signal is often a way to indicate that one entire image is transmitted. Parameter WIDTH = 768, // Image width HEIGHT = 512, // Image height INFILE = "./img/kodim01.hex", // image file START_UP_DELAY = 100, // Delay during start up time HSYNC_DELAY = 160, // Delay between HSYNC pulses VALUE = 100, // value for Brightness operation THRESHOLD = 90, // Threshold value for Threshold operation SIGN = 1 // Sign value using for brightness operation // SIGN = 0: Brightness subtraction // SIGN = 1: Brightness addition : FPGA projects for students // FPGA project: Image processing in Verilog hex file includes R, G, B data of the bitmap image. The input image size is 768x512 and the image. Below is a Matlab example code to convert a bitmap image to a. bmp image on in Verilog, the image is required to be converted from the bitmap format to the hexadecimal format. All the related questions asked by students are answered at the bottom of this article.įirst of all, Verilog cannot read images directly. In this project, I added some simple image processing code into the reading part to make an example of image processing, but you can easily remove it to get raw image data. The image writing part is also extremely useful for testing as well when you want to see the output image in BMP format. The image processing operation is selected by a "parameter.v" file and then, the processed image data are written to a bitmap image output.bmp for verification purposes. The image reading Verilog code operates as a Verilog model of an image sensor/ camera, which can be really helpful for functional verifications in real-time FPGA image processing projects. In this FPGA Verilog project, some simple processing operations are implemented in Verilog such as inversion, brightness control and threshold operations.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed